简答题

正确答案

本题是同步计数器的设计,分析步骤如下:

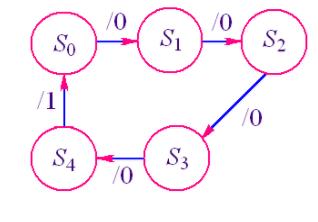

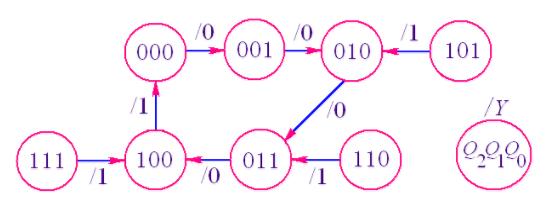

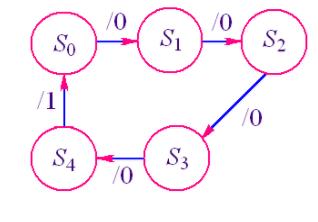

(1) 根据设计要求,设定状态,画出状态转换图。该状态图不须化简。

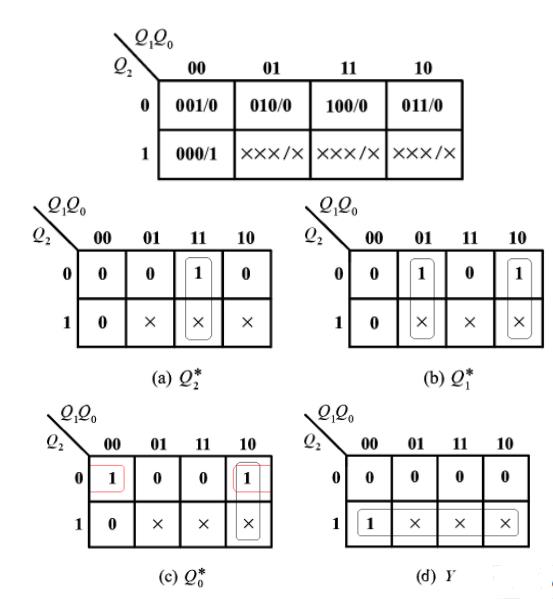

(2) 状态分配,列状态转换编码表。由题意要求M=5,故应取触发器位数n=3,

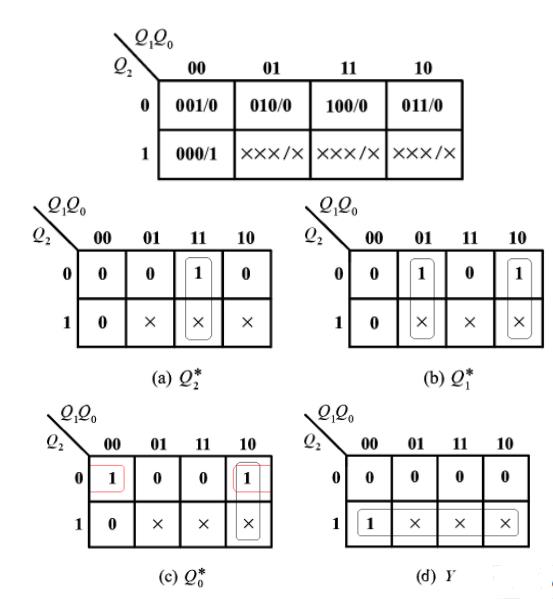

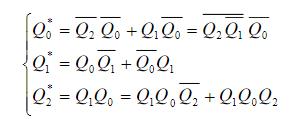

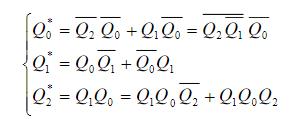

(1) 画出电路的次态卡诺图,经化简得到电路的状态方程。

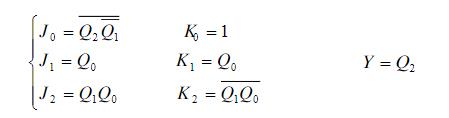

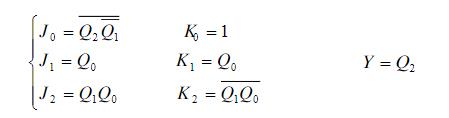

(4) 选择触发器用JK触发器,则可列出有关JK触发器驱动方程和进位输出方程。

(5)画逻辑电路图

(6)检查能否自启动

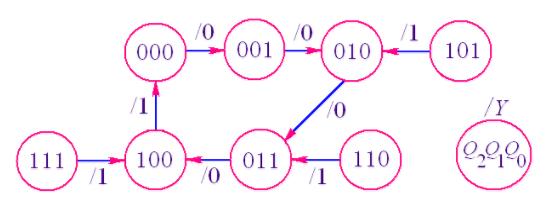

可见,如果电路进入无效状态101、110、111时,都可在CP脉冲作用下,分别进入有效状态010、011、100。所以电路能够自启动。

(1) 根据设计要求,设定状态,画出状态转换图。该状态图不须化简。

(2) 状态分配,列状态转换编码表。由题意要求M=5,故应取触发器位数n=3,

(1) 画出电路的次态卡诺图,经化简得到电路的状态方程。

(4) 选择触发器用JK触发器,则可列出有关JK触发器驱动方程和进位输出方程。

(5)画逻辑电路图

(6)检查能否自启动

可见,如果电路进入无效状态101、110、111时,都可在CP脉冲作用下,分别进入有效状态010、011、100。所以电路能够自启动。

答案解析

略